Review Article

# A review of different structures of power amplifiers to improve linearity and efficiency

#### **Fazel Ziraksaz**

Shahid Beheshti University, Tehran 1983969411, Iran; f\_ziraksaz@sbu.ac.ir

#### CITATION

Ziraksaz F. A review of different structures of power amplifiers to improve linearity and efficiency. Computer and Telecommunication Engineering. 2024; 2(1): 2305. https://doi.org/10.54517/cte.v2i1.230

#### ARTICLE INFO

Received: 21 September 2023 Accepted: 24 November 2023 Available online: 2 February 2024

#### COPYRIGHT

Copyright © 2024 by author(s). Computer and Telecommunication Engineering is published by Asia Pacific Academy of Science Pte. Ltd. This work is licensed under the Creative Commons Attribution (CC BY) license.

https://creativecommons.org/licenses/by/4.0/

**Abstract:** This review paper presents a comprehensive study of commonly used power amplifier (PA) structures. In recent years, with the development of modern wireless telecommunications and their dramatic challenges, new requirements are needed. In addition, some applications, like cell phones and tablets for example, need new considerations, especially in terms of power consumption. Also, linearity is another major factor in designing a PA. Furthermore, fabrication technologies such as complementary metal-oxide semiconductor (CMOS), silicon on insulator (SOI), gallium nitride (GaN), gallium arsenide (GaAs), etc., play a crucial role in terms of power consumption. Therefore, it is necessary for PAs to meet these considerations. This paper reviews design considerations, fabrication technologies and common PA structures including envelope tracking (ET), envelope elimination and restoration (EER), Doherty, linear amplification with nonlinear components (LINC), feedback and feedforward linearization techniques with their pros and cons. This review focuses on the significant achievements, techniques, structures and characteristics of each. Also, this review focuses on the significant achievements, techniques, structures and characteristics of each. Also, this paper tries to provide a brief overview of the various methods with the advantages and disadvantages of each. This review paper tries to make readers familiar with common structures so that readers know the advantages and disadvantages of each and choose the desired structure based on their priorities.

**Keywords:** power amplifier (PA); linearization technique; wireless telecommunication; envelope tracking (ET); envelope elimination and restoration (EER); Doherty; linear amplification with nonlinear components (LINC); feedback; feedforward; CMOS; SOI; GaN; GaAs

# 1. Introduction

The power amplifier (PA) is a crucial module of a transmitter playing a key role in the quality of the transmitted signal and total power consumption of an electronic device like cell phones and tablets, for example. PA is one of the most power-hungry building blocks in a transmitter [1]. In addition, it has an important role in linearity. Operation frequency and output power play vital roles in PAs. According to operation frequency and output power, fabrication technology is chosen. Therefore, setting priorities is crucial. In other words, factors like output power, fabrication technologies and operation frequency are crucial to designing a PA with a great performance in terms of linearity and efficient power consumption. Also, the fabrication cost and area occupation are two limiting factors in using technology. Hence, the CMOS technology is trendy. However, this technology faces output power limitation.

On the other hand, there is a constant trade-off between efficiency and linearity.

Therefore, it is necessary to find structures that can achieve the best performance in terms of linearity and efficiency simultaneously. Usually, the methods can improve one of the challenges.

Generally, PAs are divided into two categories, linear and switching structures. Typical PAs including linear and switching PAs face some problems that limit their use in new considerations, especially in terms of new linearity requirements. Linear PAs including A, B, C and AB classes provide good linearity in theory, but they cannot provide theoretical performances in practical experiments. Also, switching PAs including D, E and F classes as the prominent switching PAs provide good efficiency in theory, but they cannot present the theoretical performances in practical experiments. Thus, structures are needed that can improve the linearity and efficiency of the PAs.

Modified structures usually improve linearity or efficiency. The methods that came up to overcome the linearity problems may decrease efficiency and increase the complexity and power loss of the structures. Methods like ET, EER and LINC have been proposed with the major goal of improving efficiency [2–15], and methods such as Doherty, feedback and feedforward have come up with the main goal of improving linearity [16–19].

On the other hand, each standard imposes some requirements on the structure, so it is necessary to pay attention to them. For example, some standards like IEEE (Institute of Electrical and Electronics Engineers) 802.11.b use signals with a high peak-to-average power ratio (PAPR) around 10 dB [20] or the PAPR of the LTE is around 6–8 dB, which leads to new design considerations for achieving good linearity and efficiency. Each standard or application imposes some linearity requirements in error vector magnitude (EVM) and adjacent channel power ratio (ACPR) parameters, which are different from one standard or application to another standard or application, which creates challenges in the design of PAs. In addition, different standards employ various modulation types, leading to different effects. For instance, modulation based on non-constant envelope such as quadrature amplitude modulation (QAM) has high PAPR. High PAPR leads to extra power loss when the PA uses fixed power supply.

Choosing an appropriate technology for the PA is important in terms of its output power and operation frequency as two major factors in transmitter structure. Various technologies have been developed. Technologies like GaN, and LDMOS (Laterally Diffused Metal Oxide Semiconductor) are appropriate for high output power, for example, more than 10 W. CMOS technology is one of the best choices for integrated circuits (ICs) which has many commercial uses because of the lower cost than other technologies. However, it cannot provide high output power.

This paper reviews different considerations including standards, technologies and various structures. This paper talks about the different methods with their advantages and disadvantages. In addition, it also addresses design considerations and commonly used technologies. In other words, this review paper focuses on the significant achievements, fabrication technologies, various techniques to improve linearity and efficiency, and their features.

## 2. Considerations

Fundamentally, designing each building block involves some considerations. In power amplifiers, there is always a trade-off between linearity and efficiency. In most electronic gadgets, the issue of power consumption reduction is one of the hot topics. Therefore, the decreasing power consumption of PAs is significant.

On the other hand, standards and modulations also impose requirements on the PAs. Thus, it is necessary to know these considerations. These considerations include power consumption, linearity, standards and modulations, each with its own challenges.

# 2.1. Power consumption, linearity and technology

Power consumption and linearity are two main challenges in the design of PAs. Especially in new applications like mobile phones and other smart gadgets, power saving is one of the most popular demands from users and companies. To be more specific, in any system that includes transceivers and uses batteries, reducing power consumption and energy management are very important. Therefore, you can see the competition between companies to make energy-saving devices. Also, this trend is expected to continue in the future because using electronic devices like smart gadgets is increasing. Thus, designers and researchers have to meet this demand. PAs are one of the most power-hungry building blocks in transceivers. Hence, decreasing power loss in this block plays a vital role in the total power consumption of a device.

On the other hand, the quality of the transmitted signal is vital, especially in modern wireless telecommunications and new standards like 5G and 6G, because these standards need a certain linearity. For instance, 5G usually requires EVM (Error Vector Magnitude) to be less than 5.6%. Modern wireless communications need to meet more stringent requirements. Furthermore, because of the crowded frequency spectrum, the power amplifier has to have a high-purity frequency spectrum. Otherwise, the amplified frequency band acts as a noise for other sidebands. Therefore, the requirements related to adjacent channel power ratio (ACPR) are critical in PAs.

Applications and technologies play a crucial role in terms of power consumption and available frequency. Fabrication technologies face limitations in providing output power and operating at high frequencies. According to the design requirements in the field of output power and operation frequency, the technology should be selected. Therefore, these two factors are limiting factors in design of a PA. In smart gadgets, CMOS because of the ability to integrate and lower power consumption is a prevalent technology. Moreover, usually for smart devices or IoT, the emitted power does not exceed 2 W according to the regulations. GaN and LDMOS are popular technologies when the goal is to send data over long distances with high output power.

For output power up to 2 W and integrated circuit, complementary metal-oxide-semiconductor (CMOS) is the best choice. Silicon on insulator (SOI) is another option because this technology has very little current leakage [21]. Therefore, it is a suitable option to decrease power loss. Furthermore, because of lower parasitic capacitance compared with CMOS technology, it has a better frequency response.

But this technology suffers from heat from isolation. Although both technologies are suitable for integrated circuits, it is almost impossible to use them for an output power of more than around 2 W. This challenge is intensified especially in radio frequency (RF) signals.

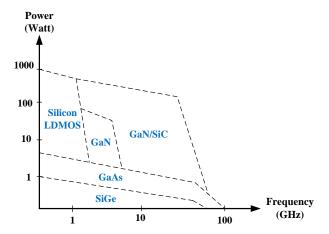

Gallium nitride (GaN) and laterally-diffused metal-oxide semiconductor (LDMOS) are two useful technologies for high-power and radio frequency applications. The frequency range of gallium arsenide (GaAs) is better, but it has a smaller output power. Although new CMOS technologies like 65 nm and beyond almost overcome the challenge of radio frequencies, the challenge of high output power still remains. **Figure 1** shows a comparison among several widely used technologies [22]. This figure somehow helps to designers regarding their own requirements choose the appropriate technology. The most important parameters in PAs are output power, supply voltage and frequency band. In the first stage, each designer must set the desirable output power and frequency band then based on these features, they can choose the appropriate technology.

Figure 1. Comparison among several widely used technologies [22].

#### 2.2. Standards and modulations

Each of the standards and each type of modulation have its own requirements and challenges.

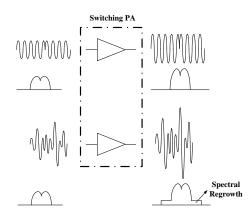

One of the influential factors in choosing the type of power amplifier is the type of signal modulation. In constant envelope modulation, it is possible to use switching and linear PAs. **Figure 2** shows using nonlinear PA for a variable envelope modulation leads to spectral regrowth [23]. Therefore, variable envelope modulations usually need linear PAs. In fact, the power efficiency of PA in the transmitter is related to the type of PA used in the transmitter, and the type of PA is related to the type of modulation.

Figure 2. The effects of switching PAs on constant and variable signals [23].

In order to achieve a high data rate with high spectral efficiency, modern wireless communication systems use a signal with a high peak to average power ratio (PAPR). For example, the PAPR of IEEE 802.11.a/b/g is around 10 dB. Also, the PAPR of 5G communication is around 10 dB [24]. Therefore, because of the high back-off in new standards, using a fixed supply limits efficiency. This challenge is one of the reasons for using variable power supply structures like ET and EER structures.

# 3. Efficiency and linearity improvement techniques

The role of a power amplifier in a transceiver is to transmit the desired signal with the least destruction. In other words, an ideal power amplifier has to be able to amplify a signal while maintaining linearity and high efficiency. Usually, classic power amplifiers cannot maintain linearity and efficiency simultaneously. Therefore, in the past decades, several methods have been developed to answer these demands. Each of the methods has its own advantages and disadvantages. Typically, these techniques are divided into two categories. The techniques that improve linearity like feedback and feedforward architectures, and the techniques improving efficiency like ET, EER and LINC structures.

## 3.1. Classic power amplifiers

Classic PAs are divided into two categories. Linear PAs provide high linearity and low efficiency. In contrast, switching PAs have high efficiency with low linearity. However, these features are in theory and the situation is different in practice. In practical situations, neither conventional linear amplifiers have good linearity, nor switching amplifiers have high efficiency. Hence, it is necessary to improve conventional PAs. **Table 1** shows a comparison between classic PAs. This table presents the features of classic power amplifiers in theory. Obviously, in practical tests, the results are much worse.

**Table 1.** Comparison among different classes.

| Class | Efficiency (%) | Conduction angle (degree) |

|-------|----------------|---------------------------|

| A     | 50             | 360                       |

| В     | ~80            | 180                       |

| AB    | 50-80          | 180–360                   |

| C     | 80–100         | <180                      |

The transistor in Class A is always on. Class-A has the highest fidelity to the main signal in the theory. In Class-C, efficiency increase with decreasing conduction angle, and it leads to reduce linearity. This class is suitable for structures like Doherty that need an auxiliary amplifier that is sometimes turned on. Class-B faces distortion caused by zero-crossing. Class-AB does not have the problem of zero-crossing distortion because of the greater conduction angle than class B. Because of using pulse shape signals in switching PAs, the conduction angle is near 0°. In theory, the efficiency of this type is near 100%. In practical tests, as a result of power loss in matching circuits and transistors, efficiency is much less than the theoretical value. Therefore, to achieve better results in terms of linearity and efficiency, classic PAs need some methods to improve the results of efficiency and linearity.

Today, classical PAs are usually used in a hybrid structure such as Doherty, LINC, ET and EER, and it is expected that the use of them alone will be less common in the future. Of course, this does not mean eliminating structures based on just a classical PA. Rather, hybrid structures are expected to play a more important role in the future.

## 3.2. Solutions for variable power supply and reducing power loss

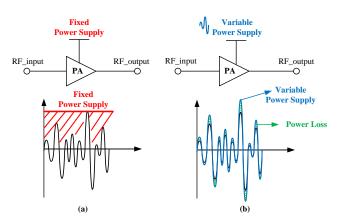

Usually, modern wireless communications use high peak-to-average power ratio (PAPR). **Table 2** shows some standards with their PAPRs [25,26]. Therefore, using a fixed power supply like conventional PAs leads to a high power loss as shown in **Figure 3a**. Thus, this approach is not efficient [27]. Hence, by using a variable power supply like **Figure 3b**, the power loss of a PA dramatically decreases.

Table 2. Standards and their PAPRs [25,26].

| Standards | Modulation type | PAPR (dB) |

|-----------|-----------------|-----------|

| 4G-LTE    | Various         | 5.5–9     |

| WiFi      | 256-QAM         | 9.6       |

| HSUPA     | 16/64-QAM       | 5–7       |

| UMTS      | QPSK            | 3–5       |

| EDGE      | 8-PSK           | 3–4       |

Figure 3. Comparison between (a) fixed; and (b) variable power supply.

Regarding some standards like mobile communications use signals with high PAPR [28], for instance the PAPR of 5G communication is around 10 dB [24]. Therefore, some methods need to be able to implement a variable power supply that can track the envelope of the signal with high accuracy in order to overcome the extra power loss. In fact, the envelope of the signal is considered as the power supply in these techniques.

Regarding **Figure 3** and **Table 2**, using a fixed supply leads to a high power loss. Therefore, some techniques like envelope tracking and envelope elimination and restoration came up using the variable power supply in order to overcome extra power dissipation.

To make a variable power supply, a block is needed. This block in ET and EER structures is called a modulator, with its own features. In other words, this block amplifies the envelope of the main input signal as a variable power supply as the supply of the main PA. The modulator must have a high slew rate, and the bandwidth of the modulator must be 4 to 5 more than the envelope bandwidth as well [1,2] to be able to track the envelope with high accuracy. Envelope tracking (ET) and envelope elimination and restoration (EER) are the two most popular structures for variable power supply structures.

## 3.2.1. Envelope elimination and restoration (EER)

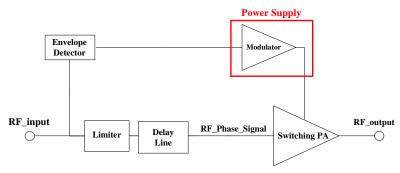

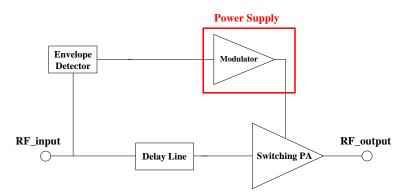

This technique was presented by Kahn on 1952 [3]. In this method, the input RF-signal (Radio Frequency) is divided two paths which is shown in **Figure 4**.

Figure 4. EER structure.

In a path, the envelope of the input signal is divided and amplified by a

modulator. This amplified signal is applied to the main PA as a variable power supply. And in the second path, the RF phase of the input signal is amplified by a switching PA. Because of using a switching PA as a main PA, this technique has a high efficiency. The main purpose of this technique is to increase efficiency in the first place.

But this technique faces some challenges in terms of linearity. As a result of using a switching PA, this structure is not suitable for a non-constant envelope. Using this structure leads to increase spectral regrowth for a variable envelope signal. Another challenge in this structure is a mismatch between the two paths. Therefore, in order to overcome this challenge to some extent, a delay line is usually used to equalize the delay between the two paths to some extent.

## 3.2.2. Envelope tracking (ET)

ET technique is a popular method to improve the efficiency of Pas [26], especially when the input signal has high PAPR [29]. In other words, ET is another technique to provide a variable power supply shown in **Figure 5**.

Figure 5. ET structure.

In contrast EER technique, this structure does not need to separate the envelope and phase of an RF-signal in the path of the main PA. Thus, to some extent, the problem of mismatch between two paths has been solved in this structure. Although, there is a delay between the two paths still. In this technique, the envelope of the RF-input signal is applied to the main PA as a variable supply. Therefore, this technique is suitable for signals with high PAPR and making variable power supply. Also, the ET structure profits a linear PA as a main amplifier that causes this technique to be able to amplify RF-signal with variable envelope. However, the efficiency of ET is less than EER. In other words, although the efficiency of ET is less than EER, the linearity performance of this structure is better.

# 3.2.3. Categories of creating a variable power supply

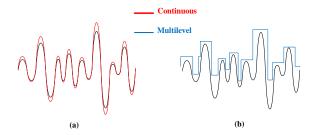

There are two main concepts to implement variable power supply in ET and EER techniques, as shown in **Figure 6**.

Figure 6. Variable power supplies (a) continuous; (b) multilevel.

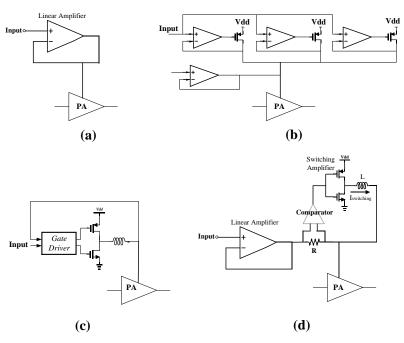

In the first method shown in **Figure 6a**, the envelope of the signal is followed momentarily, and the power supply is applied accordingly. Although this method has the least amount of losses, the complexity of the structure is more. There are three structures for implementing variable power supply including linear, switching and hybrid modulators shown in **Figure 7**.

Figure 7. ET modulator structures: (a) linear; (b) improved linear; (c) switching; (d) simple hybrid modulator [2,4,30,31].

To implement a variable power supply, a modulator is used. The linear modulator uses a linear amplifier shown in **Figure 7a**. This type has high bandwidth, but because of using linear amplifier, it suffers from low efficiency. In order to achieve high output current in the output of the modulator, some works like reference [4] use several parallel linear amplifiers to achieve a large current by summing the current of each, as shown in **Figure 7b**.

Switching modulators employ switching amplifiers. The perk of switching modulators is their high efficiency. This type usually has low bandwidth and linearity. Especially, in CMOS technology, the bandwidth is not wide because of the limiting of switching speed, though, the switching modulator is efficient [30,32,33]. The block diagram of the switching modulator is shown in **Figure 7c**.

Hybrid modulators benefit from both advantages of linear and switching

modulators. Hybrid modulators consist of a linear amplifier to track the envelope of the input signal and a switching amplifier to amplify the signal and provide the main output current [5,6]. This type of modulator can be suitable for applications with high PAPR and wide bandwidth signals [30,31,34,35]. A simple hybrid modulator is shown in **Figure 7d**.

All in all, for today's wireless communication standards, considering that they need a large bandwidth around the center frequency and also use signals with high PAPRs, a hybrid structure is the best choice to follow the signal with high accuracy and provide good efficiency. In a hybrid modulator, the linear amplifier should have a high gain-bandwidth, high slew rate, and low output impedance [1]. In order to reduce the distortion of the envelope, the bandwidth of the hybrid modulator should be 4 to 6 times higher than the bandwidth of the envelope of the input signal [2]. To track the envelope of the signal with high accuracy to decrease power loss, the minimum slew rate is defined in [36].

Slew rate =

$$2\pi \times (4 \text{ to } 6 \text{ signal } BW) \times (\frac{1}{2}V_{\text{peak-to-peak}})$$

(1)

where, BW and  $V_{\text{peak-to-peak}}$  are the bandwidth of the input signal and the maximum peak to peak voltage of the output signal.

To reduce output ripples, according to Equation (2), output impedance of linear amplifier should be low at switching frequency [1].

$$V_{\text{out ripples}} = I_{\text{switching}} \times (R_{\text{Load}} || Z_{\text{out linear amplifier}})$$

(2)

where,  $I_{\text{switching}}$ ,  $R_{\text{Load}}$  and  $Z_{\text{out\_linear amplifier}}$  are the current of switching stage, the load resistance, and the output impedance of the linear amplifier.

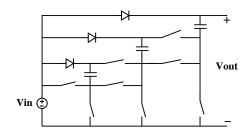

In the second method shown in **Figure 6b**, the envelope is divided into several levels and the power supply is applied according to these levels. This method is implemented by using a number of switches [7–11] and is somewhat simpler than the first method, but the amount of power loss in this method is higher. **Figure 8** shows a simple structure of this type [8].

Figure 8. A simple multilevel structure [8].

#### 3.3. A solution to overcome envelope variations

One of the challenges in some standards and modulations is using variable envelopes. Moreover, these signals usually have high PAPR, especially in 5G communications [37–39]. Therefore, several techniques are proposed to answer this challenge to be able to achieve high efficiency from peak to back-off power levels [40,41]. Some techniques such as ET and EER use a variable power supply. Some other techniques propose another method to overcome this challenge.

The main idea of these structures is to overcome changes in the envelope of the input signal. These techniques decompose a signal with a variable envelope signal

into two signals with a constant envelope with different phases. Therefore, two signals with constant envelopes are created.

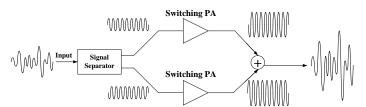

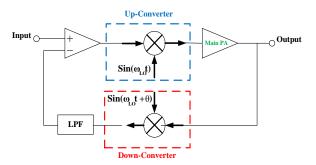

This idea titled outphasing in 1935 by Chireix was presented [12], then in 1974, a structure based on this concept called linear amplification with nonlinear components (LINC) by Cox was published [13]. Both references used this concept.

Figure 9 shows the basic concept with a block diagram.

Figure 9. Block diagram of outphasing.

This technique uses two switching PAs in each path. Therefore, in theory, the efficiency of LINC or outpacing is 100%. This technique is one of the most popular techniques to achieve high efficiency.

Implementation of this technique faces some challenges. Because of separating the main signal into two signals, there is a mismatch between the two paths leading to spectral regrowth [23]. On the other hand, losses in the output summing device lead to decrease efficiency. Designing a high-efficiency combiner plays a vital role in improving the efficiency of outphasing Pas [40]. Generally, when a structure uses several separated paths that are finally combined to create the final amplified signal, the mismatch of paths is usually problematic. Moreover, output summing devices in these structures may be led to linearity challenges. In addition, because of using the separator and summing device, implementation of LINC in CMOS integrated circuits is challenging, and besides losses and linearity challenges, they typically occupy a lot of space on the chip. Therefore, the efficiency of this structure never reaches its theoretical value. Also, the use of switching PAs increases the possibility of linearity challenges including spectral regrowth. Thus, outphasing PAs usually need to improve linearity requirements. For instance, some works [14] use linearization techniques such as pre-distortion in order to improve ACPR.

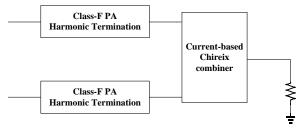

The study of Chang et al. [15] with the use of Class-F and harmonic termination as switching PAs in two paths shown in **Figure 10**, and the study of Afanasyev et al. [14] with pre-distortion technique try to improve the linearity of the structure. In the study of Afanasyev et al. [14], the error vector magnitude (EVM) of the structure has improved by about 8%.

**Figure 10.** Simplified block diagram of the proposed outphasing power amplifier [15].

#### 3.4. Solutions to improve the linearity and efficiency

## **3.4.1. Doherty**

With increasing input power, the output power of the PA increases. This increase has a certain maximum value. In other words, after a certain amount of input power, the output power of the PA is saturated. In PAs, there is a point called the 1-dB compression point (1-dBCP) which is the beginning of the nonlinear region for power amplifiers. The increase in 1-dBCP allows the PA to operate over a wider range of input power with low nonlinear effects.

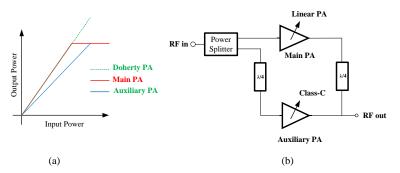

In 1935, William H. Doherty proposed a structure [16] that is still very popular because of its simplicity [42]. The main purpose of the proposed structure is that when the main amplifier is saturated, an auxiliary amplifier is added, and it causes the saturation to occur later and the PA has been high efficiency from peak to back-off power levels [42–54]. Conventional Doherty PAs are suitable for signals with 6 dB back-off [55]. **Figure 11** shows Input/output characteristics and conceptual block diagram of a Doherty PA.

**Figure 11. (a)** input/output characteristics; **(b)** conceptual block diagram of a Doherty PA.

In basic structure, a Doherty PA consists of the main amplifier (Class-A, B, AB), the peaking auxiliary PA (Class-C) and the phase adjuster (quarter-wave transmission line). In low power, the peaking amplifier is in the cut-off region and it operates as an open circuit. As the signal amplitude increases into medium and peak power, the auxiliary amplifier becomes active and prevents the drop in output power.

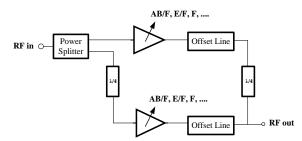

Implementation of transmission lines in CMOS Doherty PA is very challenging. Moreover, these transmission lines have considerable losses leading to decrease efficiency. Additionally, as a result of using linear PA as main and auxiliary amplifiers, conventional Doherty PAs face some challenges in terms of efficiency. Therefore, in some works [17–19], by combining amplifiers of different classes, especially switching PAs along with linear PAs, they use the advantages of each and improve efficiency and linearity at the same time. For example, using a Class F PA, by manipulating the waveforms, the structure minimizes the overlap between the voltage and current waveforms and improves efficiency [17]. The study of Nasri et al. [56] uses Class-J for main and auxiliary PAs and manipulates the waveforms. **Figure 12** shows the block diagram of an improved Doherty PA based on combining PAs. The linearity of Doherty PA can be improved by the pre-distortion technique [17]. The study of Chen et al. [42] proposes a new load modulation combiner to have the

capability of back-off control. The proposed combiner consists of two transmission lines and a shunt element. At the peak power level, the shunt element becomes virtually open-circuited. This part controls the performance of main and auxiliary amplifiers.

**Figure 12.** Block diagram of a Doherty based on combining PAs.

#### 3.4.2. Feedforward and feedback architectures

In most cases, after amplifying an RF signal by a PA, the output signal suffers from problems such as distortion and spectral regrowth. Therefore, the amplified output signal cannot meet the linearity requirements in most cases. Hence, to improve linearity requirements like EVM and ACPR, linearization techniques are needed.

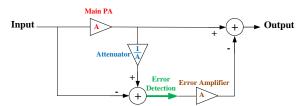

The feedforward technique has a simple and effective idea. The basic concept is that the structure computes the difference between the main signal and the amplified signal. In other words, parts of the main signal after amplifying are degraded. The purpose of this technique is to identify the degraded parts and then compare them with the main signal to produce a signal that is the amplified main signal with the best linearity [57–59].

Figure 13. Block diagram of a conceptual feedforward technique.

**Figure 13** shows the basic conceptual feedforward structure. In the first stage, the input signal must be amplified with a certain gain (A). In this section, the signal is somewhat distorted. Therefore, to eliminate the errors, it is necessary to compare with the original signal. In order to make a fair comparison, it is necessary to compare two signals with the same conditions. Hence, the amplified signal must be attenuated by the same gain  $(\frac{1}{A})$  so that the two signals have the same amplitude. By subtracting two signals from each other, the error is obtained. Now, the error is amplified by the same gain (A) then it is subtracted from the signal amplified by the main PA. Thus, the output signal is amplified without any error.

Because of using two separate paths, there is a probability of a mismatch between the two paths. Moreover, there are different time delays among paths. Therefore, the structure needs to use delay elements to synchronize paths. **Figure 14**

shows an improved feedforward architecture.

Figure 14. Block diagram of an improved feedforward architecture.

Although this technique has a good performance in theory, it suffers from some challenges. Whether the delay elements are active or passive, they introduce losses. On the other hand, the loss of the subtractors degrades the efficiency. Phase mismatch among paths and the subtractors performances lead to non-linearity [23].

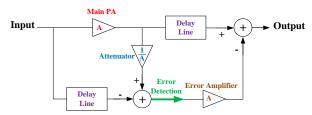

Another technique is feedback architecture. In the feedback technique, the output signal compares with the main input signal [60–62]. **Figure 15** shows the feedback architecture.

Figure 15. Feedback architecture.

In this technique, in the main path, the main signal is up-converted by a mixer then the modulated signal is amplified by a PA. The output signal is obtained with error and distortion. This technique proposes that the output signal is compared with the input signal. Hence, it is necessary to down convert frequency so that comparison is possible. Determining the phase shift in the feedback path is challenging due to the dependence on temperature and the manufacturing process [23]. Usually, feedback and feedforward are rarely used in RF and mm-wave, because they cannot handle the signal bandwidth used in today's communications like 5G.

## 5. Conclusions

This review paper presents a study of commonly used power amplifier structures, fabrication technologies, design considerations and new linearity requirements. Linearity and power consumption are the two most important requirements in many applications like cell phones and tablets for example. Fabrication technologies such as CMOS, SOI, GaN, GaAs, and LDMOS play a vital role in terms of power consumption. This paper reviews some commonly used fabrication technologies, their roles in power consumption and their pros and cons. Technologies like CMOS and SOI are suitable for smart gadgets that need ICs with

less than 2 W of output power. Because of the ability of CMOS to integrate and lower cost, it is a prevalent technology. SOI is similar to CMOS. The perk of SOI is its low current leakage leading to lower power consumption than CMOS. Moreover, because of using an isolator layer, this technology has lower parasitic capacitance compared with CMOS technology, it has a better frequency response. But this technology suffers from heat caused by isolation. GaN, GaAs and LDMOS are suitable for applications with high output power. Especially, GaN and LDMOS are popular technologies when the goal is to send data over long distances with high output power. Although the frequency range of GaAs is better, it has a smaller output power. Moreover, this review paper focuses on design considerations and linearity requirements. In modern telecommunication systems such as 5G, the PAPR of the signal is about 10 dB. Furthermore, they use complex modulations leading to high PAPR. These cause some challenges. High PAPR causes the use of a fixed power supply to lead to extra power loss. Variable power supply methods including envelope tracking (ET), envelope elimination and restoration (EER) came up to overcome the extra power consumption. Other methods such as Doherty, outphasing, and feedforward techniques focus on linearity requirements. Implementation of transmission lines in CMOS Doherty PA is very challenging. Hence, the use of it in CMOS ICs is limited. Since outphasing employs two switching amplifier in its architecture, it can achieve high efficiency. However, implementation of this technique faces some challenges. Because of separating the main signal into two signals, there is a mismatch between the two paths leading to spectral regrowth. On the other hand, losses in the output summing device lead to decrease efficiency. Because feedback and feedforward cannot handle the signal bandwidth used in today's communications like 5G, they are rarely used in RF and mm-wave.

**Conflict of interest:** The author declares no conflict of interest.

#### References

- I. Ziraksaz F, Nabavi A. Design of a Linear Class AB Amplifier with 55dB Gain, 890MHz Bandwidth and Low Output Impedance for Envelope Tracking Supply Modulator. 2019 27th Iranian Conference on Electrical Engineering (ICEE). Published online April 2019. doi: 10.1109/iraniancee.2019.8786603

- 2. Hassan M, Larson LE, Leung VW, et al. A Combined Series-Parallel Hybrid Envelope Amplifier for Envelope Tracking Mobile Terminal RF Power Amplifier Applications. IEEE Journal of Solid-State Circuits. 2012, 47(5): 1185-1198. doi: 10.1109/jssc.2012.2184639

- 3. Kahn L. Single-Sideband Transmission by Envelope Elimination and Restoration. Proceedings of the IRE. 1952, 40(7): 803-806. doi: 10.1109/jrproc.1952.273844

- 4. Kim JH, Son HS, Kim WY, et al. Envelope Amplifier with Multiple-Linear Regulator for Envelope Tracking Power Amplifier. IEEE Transactions on Microwave Theory and Techniques. 2013, 61(11): 3951-3960. doi: 10.1109/tmtt.2013.2281960

- 5. Yang SH, Chen KH, Wey CL, et al. Lossless inductor current control in envelope tracking supply modulator with self-allocation of energy for optimization of efficiency and EVM. 2016 IEEE Asian Solid-State Circuits Conference (A-SSCC), Toyama, Japan, 2016, pp. 281-284.

- 6. Paek JS, Kim D, Choo Y, et al. Design of Boosted Supply Modulator with Reverse Current Protection for Wide Battery Range in Envelope Tracking Operation. IEEE Transactions on Microwave Theory and Techniques. 2019, 67(1): 183-194. doi: 10.1109/tmtt.2018.2879323

- 7. Wang Y, Ruan X, Jin Q, et al. Quasi-Interleaved Current Control for Switch-Linear Hybrid Envelope-Tracking Power Supply. IEEE Transactions on Power Electronics. 2018, 33(6): 5415-5425. doi: 10.1109/tpel.2017.2735485

- 8. Xi H, Xu Y, Zhu Y, et al. High Bandwidth and Compact Envelope Tracking Power Supply Utilizing Switched Capacitor Topology. IEEE Access. 2019, 7: 105462-105469. doi: 10.1109/access.2019.2932607

- 9. Wang Y, Ruan X, Leng Y, et al. Hysteresis Current Control for Multilevel Converter in Parallel-Form Switch-Linear Hybrid Envelope Tracking Power Supply. IEEE Transactions on Power Electronics. 2019, 34(2): 1950-1959. doi: 10.1109/tpel.2018.2835640

- 10. He H, Ge T, Kang Y, et al. A 40 MHz Bandwidth, 91% Peak Efficiency, 2.5 W Output Power Supply Modulator With Dual-Mode Sigma–Delta Control and Adaptive Biasing Amplifier for Multistandard Communications. IEEE Transactions on Power Electronics. 2020, 35(9): 9430-9442. doi: 10.1109/tpel.2020.2969358

- 11. Xi H, Cao J, Liu N, et al. High Bandwidth Envelope Tracking Power Supply With Pulse Edge Independent Distribution Method. IEEE Transactions on Industrial Electronics. 2019, 66(8): 5907-5917. doi: 10.1109/tie.2018.2874580

- 12. Chireix H. High Power Outphasing Modulation. Proceedings of the IRE. 1935, 23(11): 1370-1392. doi: 10.1109/jrproc.1935.227299

- 13. Cox D. Linear Amplification with Nonlinear Components. IEEE Transactions on Communications. 1974, 22(12): 1942-1945. doi: 10.1109/tcom.1974.1092141

- 14. Afanasyev P, Ramabadran P, Mohammady S, et al. Phase-Only Digital Predistortion Technique for Class-E Outphasing Power Amplifiers. 2019 European Microwave Conference in Central Europe (EuMCE), 2019.

- Chang HC, Roblin P, Galaviz-Aguilar JA, et al. Asymmetrically-driven current-based chireix class-F power amplifier designed using an embedding device model. 2017 IEEE MTT-S International Microwave Symposium (IMS). Published online June 2017. doi: 10.1109/mwsym.2017.8058741

- 16. Doherty WH. A New High Efficiency Power Amplifier for Modulated Waves. Proceedings of the IRE. 1936, 24(9): 1163-1182. doi: 10.1109/jrproc.1936.228468

- 17. Meng F, Sun Y, Tian L, et al. A broadband high-efficiency doherty power amplifier with continuous inverse class-F design. 2017 XXXIInd General Assembly and Scientific Symposium of the International Union of Radio Science (URSI GASS). Published online August 2017. doi: 10.23919/ursigass.2017.8105211

- 18. Kim J. Highly Efficient Asymmetric Class-F-1/F GaN Doherty Amplifier. IEEE Transactions on Microwave Theory and Techniques. 2018, 66(9): 4070-4077. doi: 10.1109/tmtt.2018.2839195

- 19. Barakat A, Thian M, Fusco V. A High-Efficiency GaN Doherty Power Amplifier With Blended Class-EF Mode and Load-Pull Technique. IEEE Transactions on Circuits and Systems II: Express Briefs. 2018, 65(2): 151-155. doi: 10.1109/tcsii.2017.2677745

- 20. Al-akaidi M, Daoud O, Gow J. MIMO-OFDM-based DVB-H systems: a hardware design for a PAPR reduction technique. IEEE Transactions on Consumer Electronics. 2006, 52(4): 1201-1206. doi: 10.1109/tce.2006.273134

- 21. Ziraksaz F. Importance of low power electronic circuit design and its impact on energy consumption. Insight-Energy Science. 2023, 6(1): 588. doi: 10.18282/i-es.v6i1.588.

- 22. Available online: https://www.analog.com/en/analog-dialogue/articles/rf-power-amplifiers-go-wide-and-high.html (accessed on 20 December 2023).

- 23. Razavi b. RF microelectronics. Vol. 2. New York: Prentice hall, 2012.

- 24. Liu X, Jiang J, Huang C, et al. Design Techniques for High-Efficiency Envelope-Tracking Supply Modulator for 5th Generation Communication. IEEE Transactions on Circuits and Systems II: Express Briefs. 2022, 69(6): 2586-2591. doi: 10.1109/tcsii.2022.3165820

- 25. Available online:

- https://www.mpdigest.com/2019/10/23/power-amplifier-pa-designers-tackle-high-peak-to-average-power-ratio-papr-with-dig ital-predistortion-dpd/\_(accessed on 20 December 2023).

- 26. Bhardwaj S, Moallemi S, Kitchen J. A Review of Hybrid Supply Modulators in CMOS Technologies for Envelope Tracking PAs. IEEE Transactions on Power Electronics. 2023, 38(5): 6036-6062. doi: 10.1109/tpel.2022.3233441

- 27. Raab FH, Asbeck P, Cripps S, et al. Power amplifiers and transmitters for RF and microwave. IEEE Transactions on Microwave Theory and Techniques. 2002, 50(3): 814-826. doi: 10.1109/22.989965

- 28. Babu A, Shivaleelavathi BG, Yatnalli V. Efficiency Analysis and Design Considerations of a Hysteretic Current Controlled Parallel Hybrid Envelope Tracking Power Supply. Engineering, Technology & Applied Science Research. 2023, 13(1): 9812-9818. doi: 10.48084/etasr.5414

- Yerra S, Krishnamoorthy H. Multi-Phase Three-Level Buck Converter with Current Self-Balancing for High Bandwidth Envelope Tracking Power Supply. 2020 IEEE Applied Power Electronics Conference and Exposition (APEC). Published online March 2020. doi: 10.1109/apec39645.2020.9124075

- 30. Mukai K, Okabe H, Tanaka S. Recent progress in envelope tracking power amplifier for mobile handset systems. IEICE Trans. Electronics vol. E104-C, no.11, pp.516-525, Oct. 2021.

- 31. Choi J, Kim D, Kang D, Kim B. A new power management IC architecture for envelope tracking power amplifier. IEEE Trans. Microw. Theory Tech., vol. 59, no. 7, pp. 1796-1802, July 2011.

- 32. Shrestha R, van der Zee R, de Graauw A, et al. A Wideband Supply Modulator for 20 MHz RF Bandwidth Polar PAs in 65 nm CMOS. IEEE Journal of Solid-State Circuits. 2009, 44(4): 1272-1280. doi: 10.1109/jssc.2009.2014730

- 33. Wang F, Kimball DF, Lie DY, et al. A Monolithic High-Efficiency 2.4-GHz 20-dBm SiGe BiCMOS Envelope-Tracking OFDM Power Amplifier. IEEE Journal of Solid-State Circuits. 2007, 42(6): 1271-1281. doi: 10.1109/jssc.2007.897170

- 34. Li Y, Lopez J, Lie DYC, et al. Circuits and System Design of RF Polar Transmitters Using Envelope-Tracking and SiGe Power Amplifiers for Mobile WiMAX. IEEE Transactions on Circuits and Systems I: Regular Papers. 2011, 58(5): 893-901. doi: 10.1109/tcsi.2010.2089562

- 35. Yundt GB. Series-or parallel-connected composite amplifiers. IEEE Trans. Power Electron., vol. PE-1, no. 1, pp. 48-54, Jan. 1986.

- 36. Jin Q, Ruan X, Ren X, et al. Step-Wave Switched Capacitor Converter for Compact Design of Envelope Tracking Power Supply. IEEE Transactions on Industrial Electronics. 2017, 64(12): 9587-9591. doi: 10.1109/tie.2017.2716900

- 37. Wang W, Chen S, Cai J, et al., A Dual-Band Outphasing Power Amplifier Based on Noncommensurate Transmission Line Concept. IEEE Transactions on Microwave Theory and Techniques, vol. 68, no. 7, pp. 3079-3089, July 2020.

- 38. Liang C, Roblin P. The Analytic Doherty-Outphasing Power Amplifiers Continuum Theory: (Invited Paper). 2022 IEEE 22nd Annual Wireless and Microwave Technology Conference (WAMICON). Published online April 27, 2022. doi: 10.1109/wamicon53991.2022.9786088

- 39. Makhsuci S, Masoumeh Navidi S, Sanduleanu M, et al. A review of Doherty power amplifier and load modulated balanced amplifier for 5G technology. International Journal of Circuit Theory and Applications. 2023, 51(5): 2422-2445. doi: 10.1002/cta.3521

- 40. Wang W, Chen S, Cai J, et al. A high efficiency dual-band outphasing power amplifier design. International Journal of RF and Microwave Computer-Aided Engineering. 2020, 31(2). doi: 10.1002/mmce.22515

- 41. Mikrut D, Roblin P, Liang C, et al. Broadband Outphasing Power Amplifier Using Doherty-Chireix Continuum in a GaN MMIC Process. 2023 IEEE Topical Conference on RF/Microwave Power Amplifiers for Radio and Wireless Applications. Published online January 22, 2023. doi: 10.1109/pawr56957.2023.10046288

- 42. Chen Y, Choi W, Shin J, et al. New Load Modulation Combiner Having a Capability of Back-Off Control for Doherty Power Amplifiers. IEEE Access. 2023, 11: 11479-11488. doi: 10.1109/access.2023.3240649

- 43. Oh H, Kang H, Lee H, et al. Doherty Power Amplifier Based on the Fundamental Current Ratio for Asymmetric cells. IEEE Transactions on Microwave Theory and Techniques. 2017, 65(11): 4190-4197. doi: 10.1109/tmtt.2017.2701376

- 44. Kang H, Lee H, Oh H, et al. Symmetric Three-Way Doherty Power Amplifier for High Efficiency and Linearity. IEEE Transactions on Circuits and Systems II: Express Briefs. 2017, 64(8): 862-866. doi: 10.1109/tcsii.2016.2609460

- 45. Zhou J, Chen W, Chen L, et al. 3.5-GHz High-Efficiency Broadband Asymmetric Doherty Power Amplifier for 5G Applications. 2018 International Conference on Microwave and Millimeter Wave Technology (ICMMT). Published online May 2018. doi: 10.1109/icmmt.2018.8563718

- 46. Koo H, Kang H, Lee W, et al. GaN-HEMT asymmetric three-way Doherty power amplifier using GPD. IET Microwaves, Antennas & Propagation. 2018, 12(13): 2115-2121. doi: 10.1049/iet-map.2018.5464

- 47. Fang XH, Liu HY, Cheng KKM, et al. Two-Way Doherty Power Amplifier Efficiency Enhancement by Incorporating Transistors' Nonlinear Phase Distortion. IEEE Microwave and Wireless Components Letters. 2018, 28(2): 168-170. doi: 10.1109/lmwc.2017.2783845

- 48. Barthwal A, Rawat K, Koul SK. Dual Input Digitally Controlled Broadband Three-Stage Doherty Power Amplifier With Back-Off Reconfigurability. IEEE Transactions on Circuits and Systems I: Regular Papers. 2021, 68(4): 1421-1431. doi: 10.1109/tcsi.2021.3050543

- 49. Choi W, Kang H, Oh H, et al. Doherty Power Amplifier Based on Asymmetric Cells With Complex Combining Load. IEEE Transactions on Microwave Theory and Techniques. 2021, 69(4): 2336-2344. doi: 10.1109/tmtt.2021.3059666

- 50. Choi YC, Choi W, Oh H, et al. Doherty Power Amplifier With Extended High-Efficiency Range Based on the Utilization of Multiple Output Power Back-Off Parameters. IEEE Transactions on Microwave Theory and Techniques. 2022, 70(4): 2258-2270. doi: 10.1109/tmtt.2022.3144422

- 51. Chen Y, Choi W, Shin J, et al. 'Generalized expression and design method of modified load networks for Doherty power amplifier with extended back-off range. IEEE Access. 2022, 10: 77487-77497.

- 52. Saad P, Hou R. Symmetrical Load Modulated Balanced Power Amplifier With Asymmetrical Output Coupling for Load Modulation Continuum. IEEE Transactions on Microwave Theory and Techniques. 2022, 70(4): 2315-2327. doi: 10.1109/tmtt.2022.3147843

- 53. Pang J, Chu C, Wu J, et al. Broadband GaN MMIC Doherty Power Amplifier Using Continuous-Mode Combining for 5G Sub-6 GHz Applications. IEEE Journal of Solid-State Circuits. 2022, 57(7): 2143-2154. doi: 10.1109/jssc.2022.3145349

- 54. Shahmoradi M, Javid-Hosseini SH, Nayyeri V, et al. A Broadband Doherty Power Amplifier for Sub-6GHz 5G Applications. IEEE Access. 2023, 11: 28771-28780. doi: 10.1109/access.2023.3259906

- 55. Zhou X, Chan WS, Sharma T, et al. A Doherty Power Amplifier With Extended High-Efficiency Range Using Three-Port Harmonic Injection Network. IEEE Transactions on Circuits and Systems I: Regular Papers. 2022, 69(7): 2756-2766. doi: 10.1109/tcsi.2022.3160382

- 56. Nasri A, Estebsari M, Toofan S, et al. Broadband Class-J GaN Doherty Power Amplifier. Electronics. 2022, 11(4): 552. doi: 10.3390/electronics11040552

- 57. Kang SG, Lee IK, Yoo KS. Analysis and design of feedforward power amplifier. 1997 IEEE MTT-S International Microwave Symposium Digest, Denver, CO, USA, 1997, pp. 1519-1522 vol. 3.

- 58. Liao HY, Chen JH, Chiou HK, Chen CC. High-linearity CMOS feedforward power amplifier for WiMAX application. 2008 Asia-Pacific Microwave Conference, Hong Kong, China, 2008, pp. 1-4.

- 59. Borel A, Barzdėnas V, Vasjanov A. Linearization as a Solution for Power Amplifier Imperfections: A Review of Methods. Electronics. 2021, 10(9): 1073. doi: 10.3390/electronics10091073

- 60. Dawson JL, Lee TH. Cartesian feedback for RF power amplifier linearization. Proceedings of the 2004 American Control Conference. Published online 2004. doi: 10.23919/acc.2004.1383631

- 61. Dawson JL, Lee TH. Automatic phase alignment for a fully integrated cartesian feedback power amplifier system. IEEE Journal of Solid-State Circuits. 2003, 38(12): 2269-2279. doi: 10.1109/jssc.2003.819090

- 62. Dawson JL, Lee TH. Automatic phase alignment for a fully integrated CMOS Cartesian feedback power amplifier system. 2003 IEEE International Solid-State Circuits Conference, 2003. Digest of Technical Papers. ISSCC., San Francisco, CA, USA, 2003, pp. 262-492.